そのかわり、IntelからPCM Toolsというものがリリースされていて、これを使うとパフォーマンスカウンタでは見えない部分を見ることができます。ただし、プレビルドのものは配布されていないので自分でコンパイルする必要があります。

最初はVS2019でコンパイルしようとしたのですがthr/xthreadが存在しないためincludeできないと言われうまく行かず(たしかに探しても見つからない)、いろいろ試してもVS知識がなくてわからず、結局VS2017でコンパイルしたらうまくいきました。

自分用のメモとしてビルドのものを置いておきます。

PCM_201902 release.zip

ビルドするとpcm_*.exeという実行ファイルがいくつかできるのですが、有用だったのでいくつか紹介してみます。

PCI-Eの使用状況がわかるpcm-pcie

pcm-pcie.exeを実行すると以下のような出力があります。

.\pcm-pcie.exe

DEBUG: Setting Ctrl+C done.

Processor Counter Monitor: PCIe Bandwidth Monitoring Utility

This utility measures PCIe bandwidth in real-time

PCIe event definitions (each event counts as a transfer):

PCIe read events (PCI devices reading from memory - application writes to disk/network/PCIe device):

PCIePRd - PCIe UC read transfer (partial cache line)

PCIeRdCur* - PCIe read current transfer (full cache line)

On Haswell Server PCIeRdCur counts both full/partial cache lines

RFO* - Demand Data RFO

CRd* - Demand Code Read

DRd - Demand Data Read

PCIeNSWr - PCIe Non-snoop write transfer (partial cache line)

PCIe write events (PCI devices writing to memory - application reads from disk/network/PCIe device):

PCIeWiLF - PCIe Write transfer (non-allocating) (full cache line)

PCIeItoM - PCIe Write transfer (allocating) (full cache line)

PCIeNSWr - PCIe Non-snoop write transfer (partial cache line)

PCIeNSWrF - PCIe Non-snoop write transfer (full cache line)

ItoM - PCIe write full cache line

RFO - PCIe partial Write

CPU MMIO events (CPU reading/writing to PCIe devices):

PRd - MMIO Read [Haswell Server only] (Partial Cache Line)

WiL - MMIO Write (Full/Partial)

* - NOTE: Depending on the configuration of your BIOS, this tool may report '0' if the message

has not been selected.

Starting MSR service failed with error 2 Trying to load winring0.dll/winring0.sys driver...

Using winring0.dll/winring0.sys driver.

IBRS and IBPB supported : yes

STIBP supported : yes

Spec arch caps supported : no

Number of physical cores: 16

Number of logical cores: 32

Number of online logical cores: 32

Threads (logical cores) per physical core: 2

Num sockets: 2

Physical cores per socket: 8

Core PMU (perfmon) version: 3

Number of core PMU generic (programmable) counters: 4

Width of generic (programmable) counters: 48 bits

Number of core PMU fixed counters: 3

Width of fixed counters: 48 bits

Nominal core frequency: 3300000000 Hz

IBRS enabled in the kernel : no

STIBP enabled in the kernel : yes

Package thermal spec power: 130 Watt; Package minimum power: 68 Watt; Package maximum power: 200 Watt;

ERROR: QPI LL monitoring device (0:7f:8:2) is missing. The QPI statistics will be incomplete or missing.

ERROR: QPI LL monitoring device (0:7f:9:2) is missing. The QPI statistics will be incomplete or missing.

Socket 0: 1 memory controllers detected with total number of 4 channels. 0 QPI ports detected. 0 M2M (mesh to memory) blocks detected.

ERROR: QPI LL monitoring device (0:ff:8:2) is missing. The QPI statistics will be incomplete or missing.

ERROR: QPI LL monitoring device (0:ff:9:2) is missing. The QPI statistics will be incomplete or missing.

Socket 1: 1 memory controllers detected with total number of 4 channels. 0 QPI ports detected. 0 M2M (mesh to memory) blocks detected.

Detected Intel(R) Xeon(R) CPU E5-2667 v2 @ 3.30GHz "Intel(r) microarchitecture codename Ivy Bridge-EP/EN/EX/Ivytown" stepping 4 microcode level 0x42c

Update every 1 seconds

delay_ms: 54

Skt | PCIeRdCur | PCIeNSRd | PCIeWiLF | PCIeItoM | PCIeNSWr | PCIeNSWrF

0 507 K 0 0 0 0 0

1 168 0 0 1080 0 0

-----------------------------------------------------------------------------------

* 507 K 0 0 1080 0 0

Skt | PCIeRdCur | PCIeNSRd | PCIeWiLF | PCIeItoM | PCIeNSWr | PCIeNSWrF

0 501 K 0 0 0 0 0

1 552 0 0 12 0 0

-----------------------------------------------------------------------------------

* 501 K 0 0 12 0 0

....

最初は各値が何を意味しているのかわかりませんでしたが、よく見ると実行すると最初に出力されるところに意味が書いてありました。気にするべきは PCIeRdCurとPCIeItoMで、PCIeRdCurはPCIE→ CPU/メインメモリへの読み取り(ホスト側から見て書き込み)で、 PCIeItoMはPCIE→CPU/メインメモリへの書き込み(ホスト側から見て読み込み)のようです。

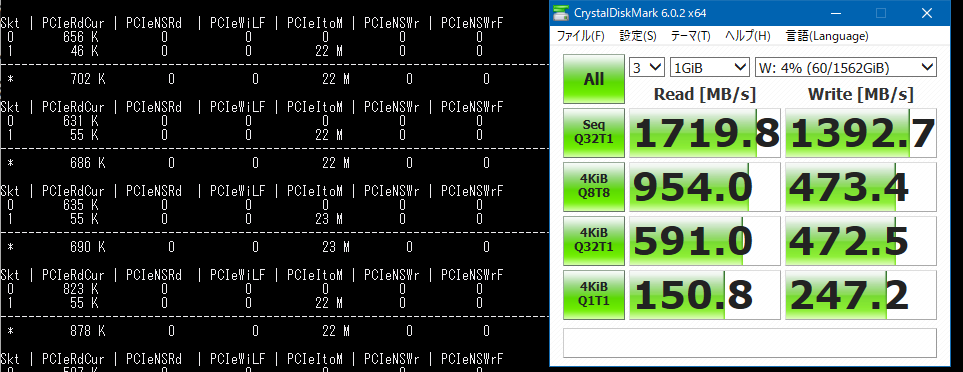

例として、ソケット2配下のPCIEに接続されているnvme(U.2フォームファクタ)へのベンチマーク中にとった値は、CDMの読み込みで1719MB/sと出ましたがPCMの方では23Mとなりました。

この23Mというのが何を意味しているかというと、1秒間に23M回要求があったということらしいです。これらからI/Oのサイズを求めると (1719.8 MB/s) / 23MHz となり、IOサイズは約74バイトという計算になります(計算はグーグル先生におまかせ)。

いろいろ調べると、PCI-EのパケットサイズはボードのTransaction Layer Packet (TLP)宣言によって16から4094バイト(2^4 -2^12) で送信できるらしいのですが、そうなると微妙に合いません。

逆に1719MB/sを64バイトで達成するには一秒間あたり26MHzの要求が必要になり、これもまた微妙に合いません。謎ですが、多分サンプリング間隔やCDMの帯域集計などのズレが有るのでしょう…。

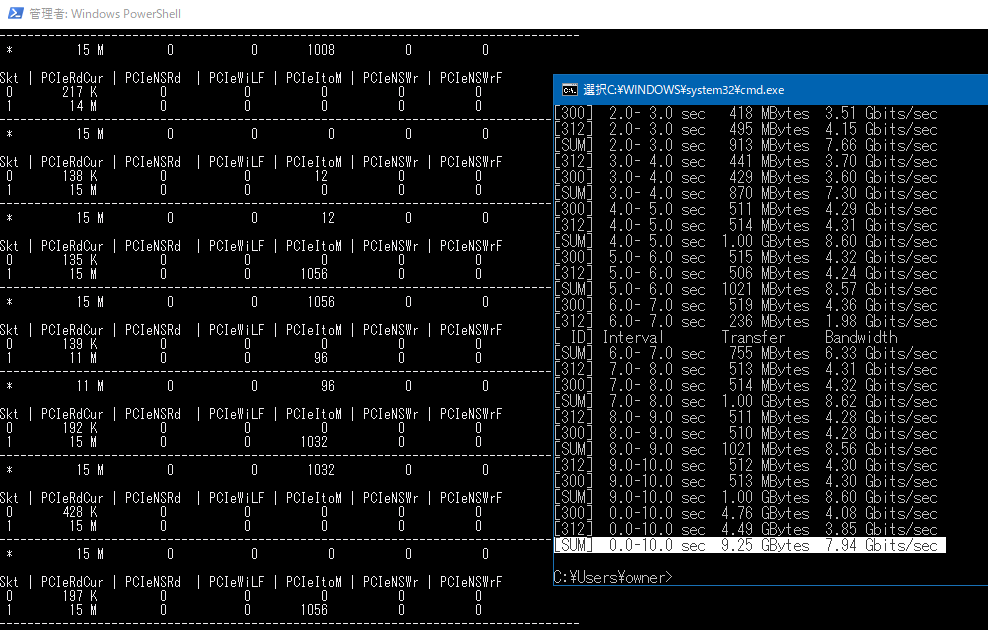

また、別のケースとして(これも余ったから)使用している10GカードのConnectX2-ENから別の物理マシンへiperfしたところ、 8.25 GBytes (7.08 Gbits/sec)の速度が出たのですが、この際のpcm-pcieの値は以下のようでした。

これに64バイトをかけると15MHz*64Byte=7680 Mbpsとなり、やはり近い値が出ているようです。

X9DAiのマニュアルによると、パケットサイズを256byte、ReadReqデータサイズは4kまで拡大できるらしいのですが、これを拡張しても特に要求回数が減ることはなかったので謎です。Linuxではlspciコマンドをvvvなどで実行すると出てくるDevCapがカード自体のケーパビリティ、DevCtlが実際にネゴシエートしている値として取得できるのですが、Windows上ではどのように動いているか不明です。逆にLinux上では64バイトという値はなかったので本当にこの計算があっているのか不安です…。

参考:

https://community.mellanox.com/s/article/understanding-pcie-configuration-for-maximum-performance#jive_content_id_PCIe_Max_Payload_Size

ちなみに、この確認の中で知ったのですが、X9DAiは各スロットでx16をx4x4x4x4などへ分割するPCIE Bifurcationに対応していたので、x16スロットにASUSのULTRA QUAD M.2 CARDのようなPLXのスイッチングチップを持たないnvme4枚刺しのカードを刺しても使えるようです。おそらくもともとはライザーカード対応のための機能だと思いますが…。

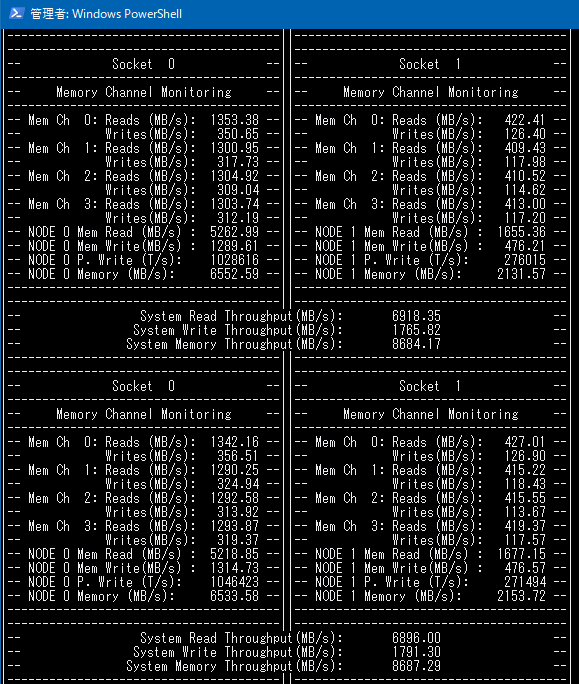

使用中のメモリ帯域がわかるpcm-memory.exe

このプログラムはなかなか有用で、チャンネルごとのメモリ帯域がわかります。

メモリ帯域のベンチマークを回すとシングルスレッドで12GB/s、4チャンネルあるのでマルチスレッドでコアあたり48GB/s、ソケット合計88GB/sという速度が出ましたが、ゲームをやっている限りせいぜい7-9GB/s程度の要求だったのでメモリ帯域についてはまだボトルネックではないということがわかりました。

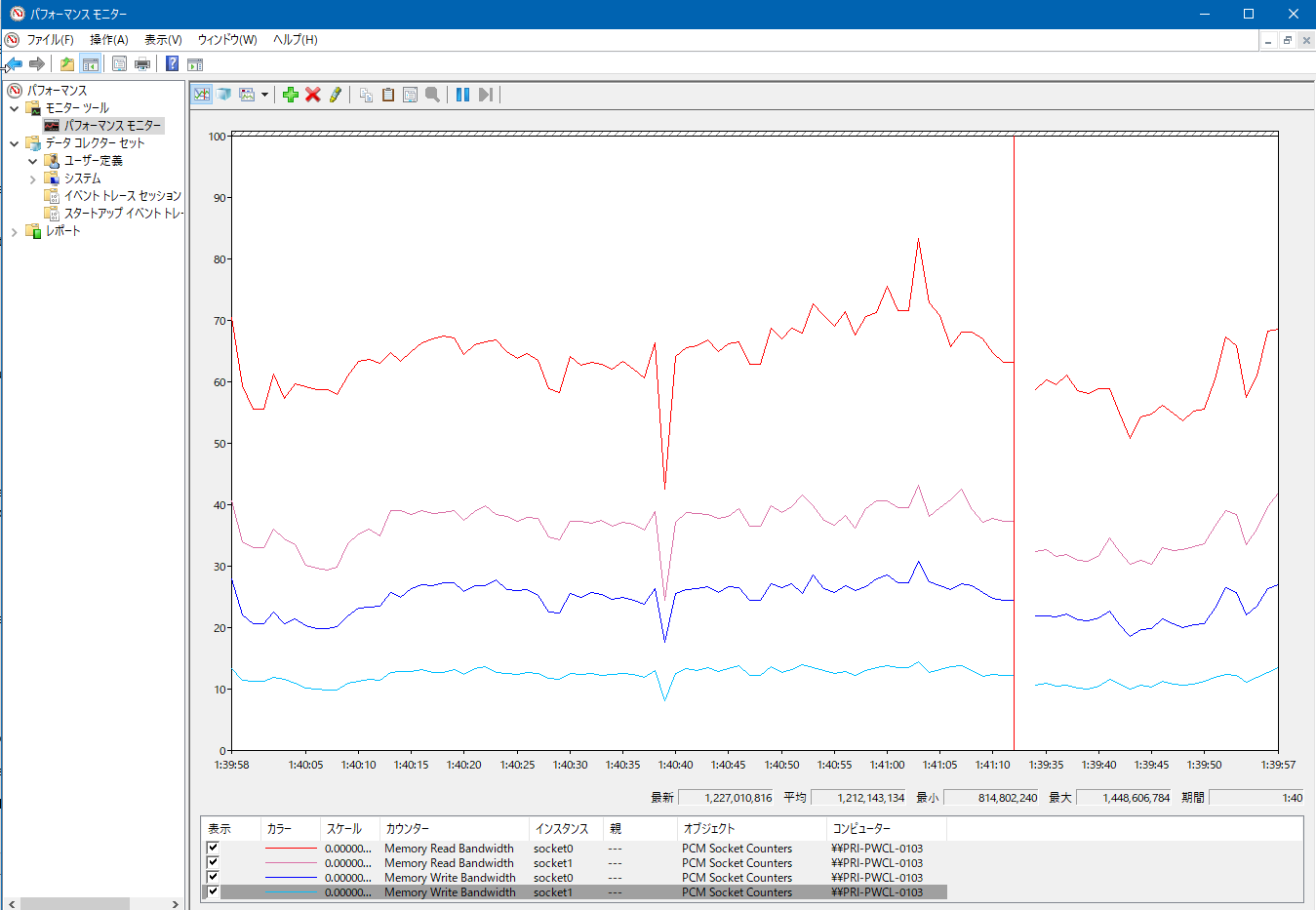

メモリ帯域などをパフォーマンスモニターで見られるPCM-Service.exe

pcm-memory.exeをパフォーマンスモニターのグラフで見るためのサービスです。管理者権限でPCM-Service.exe -InstallでインストールするとProcessor Counter Monitor Serviceというサービスが追加され、これを開始するとパフォーマンスカウンターにPCM_*が追加されます。

これらのパフォーマンスモニタリングから、最終的な結論としてXeon E5 2667v2は足回りはまだ余裕があるもののコアあたりの性能をあげないとゲームにおいてより良いパフォーマンスを得られないということがわかりました。感覚的にわかっていましたが…。

ただ、Zen2やCore i7系のCPUだと、使っているインターフェースカード的にPCIEのレーン数が足りないので、その点QPI跨いでしまってもレーン数の多いE5系は使いやすいんですよね…。

レガシーハードウェアが多いのでPCIE4.0を3.0にダウングレードしてそのかわりレーン数を倍にするスイッチングチップなどがあると嬉しいのですが、そんなニッチなものが売れるとは思えないですし、コスト的にも割に合わないと思うので厳しいです。Xeon Wシリーズがほしいのですが高い…。

人間は迷うと現状維持を選ぶらしいですが、今回もそうなりそうです。

[ 1 コメント ] ( 482 回表示 ) | このエントリーのURL |

<<最初へ <戻る | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 進む> 最後へ>>